Cyrix 6x86

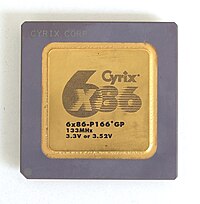

A Cyrix 6x86-P166 processor | |

| General information | |

|---|---|

| Launched |

|

| Discontinued |

|

| Marketed by | |

| Common manufacturers | |

| Performance | |

| Max. CPU clock rate | 80 MHz to 333 MHz |

| FSB speeds | 40 MHz to 100 MHz |

| Cache | |

| L1 cache |

|

| Architecture and classification | |

| Application | Desktop |

| Microarchitecture | 6x86 |

| Instruction set | x86-16, IA-32 |

| Physical specifications | |

| Transistors |

|

| Cores |

|

| Sockets | |

| Products, models, variants | |

| Core names |

|

| Variant |

|

| History | |

| Predecessor | Cyrix 5x86 |

| Successor | Cyrix III |

The Cyrix 6x86 is a line of sixth-generation, 32-bit x86 microprocessors designed and released by Cyrix in 1995. Cyrix, being a fabless company, had the chips manufactured by IBM and SGS-Thomson.[1][2] The 6x86 was made as a direct competitor to Intel's Pentium microprocessor line, and was pin compatible. During the 6x86's development, the majority of applications (office software as well as games) performed almost entirely integer operations. The designers foresaw that future applications would most likely maintain this instruction focus. So, to optimize the chip's performance for what they believed to be the most likely application of the CPU, the integer execution resources received most of the transistor budget. This would later prove to be a strategic mistake, as the popularity of the P5 Pentium caused many software developers to hand-optimize code in assembly language, to take advantage of the P5 Pentium's tightly pipelined and lower latency FPU. For example, the highly anticipated first-person shooter Quake used highly optimized assembly code designed almost entirely around the P5 Pentium's FPU. As a result, the P5 Pentium significantly outperformed other CPUs in the game.[3][4][5][6]

History

[edit]The 6x86, previously under the codename "M1" was announced by Cyrix in October 1995.[2][7][8][9][10] On release only the 100 MHz (P120+) version was available, but a 120 MHz (P150+) version was planned for mid-1995 with a 133 MHz (P166+) model later. The 100 MHz (P120+) 6x86 was available to OEMs for a price of $450 per chip in bulk quantities.[11]

In mid February 1996 Cyrix announced the P166+, P150+, and P133+ to be added to the 6x86 model line.[12] IBM, who produced the chips, also announced they will be selling their own versions of the chips.[13]

The 6x86 P200+ was planned for the end of 1996,[12] and ended up being released in June.[14]

The M2 (6x86MX) was first announced to be in development in mid 1996. It would have MMX and 32-bit optimization. The M2 would also have some of the same features as the Intel Pentium Pro such as register renaming, out-of-order completion, and speculative execution. Additionally it would have 64 KB of cache over the original 6x86 and Pentium Pro's 16 KB.[15] In March 1997 when asked about when the M2 line of processors would begin shipping, Cyrix UK managing director Brendan Sherry stated, "I've read it's going to be May but we've said late Q2 all along and I'm pretty sure we'll make that."[16]

The 6x86L was first released in January 1997 to address the heat issues with the original 6x86 line.[17] The 6x86L had a lower V-core voltage and required a split power plane voltage regulator.

In April 1997 the first laptop to use the 6x86 processor was put on sale. They were sold by TigerDirect and had a 12.1in DSTN display, 16 MB of memory, 10x CD-ROM, 1.3 GB hard disk drive, and cost $1,899 for the base price.[18]

Later by the end of May 1997 on the 27th, Cyrix said they would announce details of the new chip line (6x86MX) the day before Computex in June 1997.[19] For the low end of the series, the PR166 6x86MX was available for $190 with higher end PR200 and PR233 versions available for $240 and $320.[20][21] IBM being the producer of Cyrix's chips, would also sell their own version. Cyrix hoped to ship tens of thousands within June 1997 with up to 1 million by the end of the year. Cyrix also expected to release a 266 MHz chip by the end of 1997 and a 300 MHz in the first quarter of 1998.[22] They had slightly better floating point performance, which cut adding and multiply times by a third, but it was still slower than the Intel Pentium. The M2 also had full MMX instructions, 64 KB of cache over the original 16 KB, and had a lower core voltage of 2.5V over 3.3V of the original 6x86 line.[23][24]

National Semiconductor acquired Cyrix in July 1997.[25][26][27] National Semiconductor was not interested in high performance processors but rather system on a chip devices, and wanted to shift the focus of Cyrix to the MediaGX line.[28]

In January 1998 National Semiconductors produced a 6x86MX processor on a 0.25 micron process technology. This reduced the chip size from 150 square millimeters to 88.[29] National shifted their production of the MII and MediaGX to 0.25 by August.[30]

In September 1998 IBM's licensing partnership with Cyrix was said to be ended by National Semiconductors.[31][32] This was due to National wanting to increase production of Cyrix chips in their own facilities, and because having IBM produce Cyrix's chips was causing issues such as profit losses due to IBM frequently pricing their versions of Cyrix's chips lower.[33] National would be paying $50–55 million to IBM to end the partnership, which would end the following April. National would then be moving chip production to their own facility in South Portland, Maine.[34][35]

The Cyrix MII was released in May 1998. These chips were not exciting like people had hoped, as they were just a rebranding of the 6x86MX.[36] In December these chips cost $80 for a MII-333, $59 for a MII-300, $55 for a MII-266, and $48 for a MII-233.[37]

In May 1999 National Semiconductor decided to leave the PC chip market due to significant losses, and put the Cyrix CPU division up for sale.[38][25]

VIA bought the Cyrix line in June 1999, and ended the development of high performance processors. The MII-433GP would be the last processor produced by Cyrix.[39] Additionally after VIA's acquisition, the 6x86/L was discontinued, but the 6x86MX/MII line continued to be sold by VIA.[40][41]

VIA would continue to produce the MII throughout the early 2000s. It was expected to be discontinued when the VIA Cyrix MII was released.[42] However, the MII was still available for sale until mid/late 2003, being shown on VIA's website as a product until October, and it still saw use in devices such as network computers.[43][44]

Architecture

[edit]

The 6x86 is superscalar and superpipelined and performs register renaming, speculative execution, out-of-order execution, and data dependency removal.[45] However, it continued to use native x86 execution and ordinary microcode only, like Centaur's Winchip, unlike competitors Intel and AMD which introduced the method of dynamic translation to micro-operations with Pentium Pro and K5. The 6x86 is socket-compatible with the Intel P54C Pentium, and was offered in six performance levels: PR 90+, PR 120+, PR 133+, PR 150+, PR 166+ and PR 200+. These performance levels do not map to the clock speed of the chip itself (for example, a PR 133+ ran at 110 MHz, a PR 166+ ran at 133 MHz, etc.).[46]

With regard to internal caches, it has a 16-KB primary cache and a fully associative 256-byte instruction line cache is included alongside the primary cache, which functions as the primary instruction cache.[45]

The 6x86 and 6x86L were not completely compatible with the Intel P5 Pentium instruction set and are not multi-processor capable. For this reason, the chip identified itself as an 80486 and disabled the CPUID instruction by default. CPUID support could be enabled by first enabling extended CCR registers then setting bit 7 in CCR4. The lack of full P5 Pentium compatibility caused problems with some applications because programmers had begun to use P5 Pentium-specific instructions. Some companies released patches for their products to make them function on the 6x86.

Compatibility with the Pentium was improved in the 6x86MX, by adding a Time Stamp Counter to support the P5 Pentium's RDTSC instruction.[47] Support for the Pentium Pro's CMOVcc instructions were also added.[47]

Performance

[edit]Similarly to AMD with their K5 and early K6 processors, Cyrix used a PR rating (Performance Rating) to relate their performance to the Intel P5 Pentium (pre-P55C), as the 6x86's higher per-clock performance relative to a P5 Pentium could be quantified against a higher-clocked Pentium part. For example, a 133 MHz 6x86 will match or outperform a P5 Pentium at 166 MHz, and as a result Cyrix could market the 133 MHz chip as being a P5 Pentium 166's equal. However, the PR rating was not an entirely truthful representation of the 6x86's performance.[48]

While the 6x86's integer performance was significantly higher than P5 Pentium's, its floating point performance was more mediocre—between 2 and 4 times the performance of the 486 FPU per clock cycle (depending on the operation and precision). The FPU in the 6x86 was largely the same circuitry that was developed for Cyrix's earlier high performance 8087/80287/80387-compatible coprocessors, which was very fast for its time—the Cyrix FPU was much faster than the 80387, and even the 80486 FPU. However, it was still considerably slower than the new and completely redesigned P5 Pentium and P6 Pentium Pro-Pentium III FPUs. One of the main features of the P5/P6 FPUs is that they supported interleaving of FPU and integer instructions in their design, which Cyrix chips did not integrate. This caused very poor performance with Cyrix CPUs on games and software that took advantage of this.[49][50]

Therefore, despite being very fast clock by clock, the 6x86 and MII were forced to compete at the low-end of the market as AMD K6 and Intel P6 Pentium II were always ahead on clock speed. The 6x86's and MII's old generation "486 class" floating point unit combined with an integer section that was at best on-par with the newer P6 and K6 chips meant that Cyrix could no longer compete in performance.

Models and variants

[edit]6x86

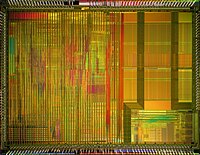

[edit]The 6x86 (codename M1) was released by Cyrix in 1996. The first generation of 6x86 had heat problems. This was primarily caused by their higher heat output than other x86 CPUs of the day and, as such, computer builders sometimes did not equip them with adequate cooling. The CPUs topped out at around 25 W heat output (like the AMD K6), whereas the P5 Pentium produced around 15 W of waste heat at its peak. However, both numbers would be a fraction of the heat generated by many high performance processors, some years later. Shortly after the original M1, the M1R was released. The M1R was a switch from SGS-Thomson 3M process to IBM 5M process, making the 6x86 chips 50% smaller.

-

Early Cyrix 6x86 (M1) die shot

6x86L

[edit]The 6x86L (codename M1L) was later released by Cyrix to address heat issues; the L standing for low-power. Improved manufacturing technologies permitted usage of a lower Vcore. Just like the Pentium MMX, the 6x86L required a split power plane voltage regulator with separate voltages for I/O and CPU core.

-

Cyrix 6x86L (M1L) die shot

6x86MX / MII

[edit]Another release of the 6x86, the 6x86MX, added MMX compatibility along with the EMMI instruction set, improved compatibility with the Pentium and Pentium Pro by adding a Time Stamp Counter and CMOVcc instructions respectively, and quadrupled the primary cache size to 64 KB. The 256-byte instruction line cache can be turned into a scratchpad cache to provide support for multimedia operations.[47] Later revisions of this chip were renamed MII, to better compete with the Pentium II processor. 6x86MX / MII was late to market, and couldn't scale well in clock speed with the manufacturing processes used at the time.

-

Cyrix 6x86MX (M2) die shot

Model table

[edit]| Images | Model | Core name | Process size (μm) |

Die area (mm2) |

Number of transistors (millions) |

Socket(s) | Package | Core Voltage | TDP (W) | Clock speed | Bus Speed | L1 Cache | Price (USD) | Launch |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PR90+ | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | 15.5 | 80 MHz | 40 MHz | 16 KB | $84 | Nov 1995 | |

| PR120+ | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | $450 | Oct 1995 | |

| PR133+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3 | 19.1 | 110 MHz | 55 MHz | 16 KB | $326 | 2-5-1996 | |

| PR150+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 20.1 | 120 MHz | 60 MHz | 16 KB | $451 | 2-5-1996 | |

| PR166+ | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | $621 | 2-5-1996 | |

| PR200+ | M1R | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | 17.13 | 150 MHz | 75 MHz | 16 KB | $499 | 6-6-1996 | |

| L-PR120+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | Jan-1997 | |

| L-PR133+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 110 MHz | 55 MHz | 16 KB | ? | Feb-1997 | |

| L-PR150+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | ? | 120 MHz | 60 MHz | 16 KB | ? | Mar-1997 | |

| L-PR166+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | 15.98 | 133 MHz | 66 MHz | 16 KB | ? | Apr-1997 | |

| L-PR200+ | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8/3.3 | 17.13 | 150 MHz | 75 MHz | 16 KB | ? | Apr-1997 | |

| PR166-MMX | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? |

133 MHz

150 MHz |

66 MHz

60 MHz |

64 KB | $190

? |

5-30-97

Q2 1998 | |

| PR200-MMX | MII | 0,35 (IBM)

0,30 (NS) |

197

156 |

6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? |

150 MHz

166 MHz |

75 MHz

66 MHz |

64 KB | $240

? |

5-30-97

Q2 1998 | |

| PR233-MMX | MII | 0,35 (IBM)

0,30 (NS) |

197

156 |

6.0 | Socket 7 | CPGA | 2.9/3.3 | ?

? |

188 MHz

200 MHz |

75 MHz

66 MHz |

64 KB | $320

? |

5-30-97

Q2 1998 | |

| PR266-MMX | MII | 0,35 (IBM)

0,30 (NS) |

197

156 |

6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | $180

? |

3-19-98

Q2 1998 | |

| MII-300-MMX (*m) | MII | 0,30

0,25 |

156

88 |

6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) |

?

? |

233 MHz

225 MHz |

66 MHz

75 MHz |

64 KB | $180

? |

4-14-98

Q1 1999 | |

| MII-333-MMX (*m) | MII | 0,30

0,25 |

156

88 |

6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) |

?

? |

250 MHz | 100 MHz

83 MHz |

64 KB | $180

? |

6-15-98

Mar-1999 | |

| MII-350-MMX | MII | 0,25 | 88 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 270 MHz

250 MHz |

90 MHz

83 MHz |

64 KB | ?

? |

?

? | |

| MII-366-MMX | MII | 0,25 | 88 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 250 MHz | 100 MHz | 64 KB | ? | Mar-1999 | |

| MII-400-MMX (*m) | MII | 0,18 | 65 | 6.0 | Super 7 | CPGA | 2.2/3.3 | ? | 285 MHz | 95 MHz | 64 KB | ? | Jun-1999 | |

| MII-433-MMX (*m) | MII | 0,18 | 65 | 6.0 | Super 7 | CPGA | 2.2/3.3 | ? | 300 MHz | 100 MHz | 64 KB | ? | Jun-1999 | |

| SGS-Thomson 6x86 Models | ||||||||||||||

| ST6x86P90+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 17.39 | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| ST6x86P120+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 19.98 | 100 MHz | 50 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P133+HS | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.52 | 21.46 | 110 MHz | 55 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P150+HS | M1 | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P166+HS | M1 | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.52 | ? | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| ST6x86P200+HS | M1 | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| IBM 6x86 Models | ||||||||||||||

| 2V2100 GB | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 80 MHz | 40 MHz | 16 KB | ? | ? | |

| 2V2P120GC | M1 | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.3 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2120 GB | M1R | 0,65 | 394 | 3.0 | Socket 7 | CPGA | 3.33 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2V2P150GE | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | ? | 120 MHz | 60 MHz | 16 KB | ? | 2-5-1996 | |

| 2V2P166GE | M1R | 0,65 | 225 | 3.0 | Socket 7 | CPGA | 3.3/3.52 | 21.8 | 133 MHz | 66 MHz | 16 KB | ? | 2-5-1996 | |

| 2V7P200GE | M1R | 0,44 | ? | 3.0 | Socket 7 | CPGA | 3.52 | 14 | 150 MHz | 75 MHz | 16 KB | ? | 2-5-1996 | |

| 2VAP120 GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 100 MHz | 50 MHz | 16 KB | ? | ? | |

| 2VAP150 GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 120 MHz | 60 MHz | 16 KB | ? | ? | |

| 2VAP166 GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 133 MHz | 66 MHz | 16 KB | ? | ? | |

| 2VAP200 GB | M1L | 0,35 | 169 | 3.0 | Socket 7 | CPGA | 2.8 | ? | 150 MHz | 75 MHz | 16 KB | ? | ? | |

| AVAPR166 GB | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 133 MHz | 66 MHz | 64 KB | $202 | 5-30-97 | |

| ? | MII | 0,35 | 197 | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 60 MHz | 64 KB | ? | 5-30-97 | |

| BVAPR200 GB | MII | 0,35 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 150 MHz | 75 MHz | 64 KB | $369 | 5-30-97 | |

| AVAPR200GA | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 66 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR233GC | MII | 0,35 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 166 MHz | 83 MHz | 64 KB | $477 | 5-30-97 | |

| AVAPR233 GB | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 188 MHz | 75 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR233GD | MII | 0,30 | ? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 200 MHz | 66 MHz | 64 KB | ? | Q2 1998 | |

| BVAPR266GE | MII | 0,35

0,30 |

? | 6.0 | Socket 7 | CPGA | 2.9/3.3 | ? | 208 MHz | 83 MHz | 64 KB | ? | 3-19-98

Q2 1998 | |

| CVAPR300GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 225 MHz | 75 MHz | 64 KB | $217 | 3-19-98 | |

| DVAPR300GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 233 MHz | 66 MHz | 64 KB | ? | ? | |

| CVAPR333GF (*m) | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3

2.2 (*m) |

? | 250 MHz | 83 MHz | 64 KB | $299 | 3-19-98 | |

| ? | MII | 0,25 | 119 | 6.0 | Super 7 | CPGA | 2.9/3.3 | ? | 263 MHz | 75 MHz | 64 KB | ? | ? | |

| ? - Missing information

*m -Available in mobile version for laptops Information From: | ||||||||||||||

Timeline

[edit]| Timeline of Cyrix Products |

|---|

|

See also

[edit]Competitors

[edit]References

[edit]- ^ Slater, Michael (May 28, 1996). "Beyond the Pentium; Intel's top challengers have reached the Pentium level, but do they pose a threat to the king of the CPU hill? We examine the chips and vendors to find out". PC Mag. Vol. 15, no. 10. Ziff Davis, Inc. pp. 100–102. ISSN 0888-8507. Retrieved March 30, 2022.

- ^ a b "CYRIX CLAIMS ITS 100MHZ 6X86 CLONE IS THE FASTEST". TechMonitor. October 9, 1995. Retrieved April 25, 2022.

- ^ Potoroaca, Adrian (December 30, 2021). "Cyrix: Gone But Not Forgotten; Peak Cyrix Through the Lens of Quake". TechSpot. Retrieved April 5, 2022.

- ^ Proven, Liam (June 5, 2016). "The rise & fall of the first real x86 rival to Intel: the Cyrix 6x86". Liam On Linux. Archived from the original on April 22, 2021. Retrieved April 5, 2022.

- ^ Shimpi, Anand (April 8, 1997). "Cyrix 6x86 MX". AnandTech. Retrieved April 7, 2022.

- ^ Sood, Yatharth (July 24, 2020). "How did a single game lead to the shake-up of an entire industry, and sounded the death knell of an entire corporation?". Medium. Retrieved April 7, 2022.

- ^ Metz, Cade (May 28, 1996). "First Cyrix 6x86 PCs: How Good? How Fast?". PC Mag. Vol. 15, no. 10. Ziff Davis, Inc. p. 112. ISSN 0888-8507. Retrieved April 1, 2022.

- ^ Vijayan, Jaikumar (October 16, 1995). "Cyrix unveils Pentium-rival chips". Computerworld. Vol. 29, no. 42. IDG Enterprise. ISSN 0010-4841. Retrieved April 4, 2022.

- ^ Minasi, Mark (2004). The Complete PC Upgrade and Maintenance Guide. Wiley (published March 9, 2004). p. 56. ISBN 9780782143102. Retrieved April 4, 2022.

- ^ "Cyrix introduces chip to challenge Pentium". News Record. October 8, 1995. p. 36. Retrieved April 27, 2022.

- ^ Metz, Cade (December 5, 1995). "Cyrix's Sixth-Generation Chip; The 6x86 targets mainstream desktops". PC Mag. Vol. 14, no. 21. Ziff Davis, Inc. p. 29. ISSN 0888-8507. Retrieved April 1, 2022.

- ^ a b Fisco, Richard (July 1996). "The Perfect Processor". PC Mag. Vol. 15, no. 13. Ziff Davis, Inc. pp. 135–136. ISSN 0888-8507. Retrieved April 4, 2022.

- ^ Vijayan, Jaikumar (February 19, 1996). "Closing in on performance; Intel competitors nip at Pentium's heels". Computerworld. Vol. 30, no. 8. IDG Enterprise. p. 42. ISSN 0010-4841. Retrieved April 1, 2022.

- ^ "Chronology of the Processor". HWM. SPH Magazines. January 2003. p. 45. ISSN 0219-5607. Retrieved April 5, 2022.

- ^ Metz, Cade (July 1996). "Cyrix's Bold M2 Strategy; Upcoming chip simplifies the upgrade decision". PC Mag. Vol. 15, no. 13. Ziff Davis, Inc. p. 36. ISSN 0888-8507. Retrieved April 4, 2022.

- ^ Veltech, Martin (March 26, 1997). "M2 bang on time - Cyrix; Cyrix's M2 processor is getting ready to join the coming out party for a new generation of processors". ZDnet. Archived from the original on April 5, 2022. Retrieved April 5, 2022.

- ^ Hare, Chris (July 14, 2008). "586/686 Processors Chart". PC Hardware Links. Retrieved April 27, 2022.

- ^ Crothers, Brooke (April 24, 1997). "First Cyrix 6x86 notebook ships". Cnet. Retrieved May 3, 2022.

- ^ Veltech, Martin (May 27, 1997). "Cyrix to announce M2 next week; Cyrix is expected to make the formal announcement of its M2 processor next week". ZDnet. Archived from the original on April 5, 2022. Retrieved April 4, 2022.

- ^ "Cyrix Launches 6x86MX Processor". EETimes. June 2, 1997. Retrieved April 5, 2022.

- ^ Miller, Greg (May 30, 1997). "Intel Facing Another Rival to Pentium II". The Los Angeles Times. Retrieved April 25, 2022.

- ^ Crothers, Brooke (May 30, 1997). "Cyrix introduces MMX chip; The 6x86MX will be a fast but cheap weapon in Cyrix's assault on the traditional processor pricing structure". Cnet. Archived from the original on April 5, 2022. Retrieved April 4, 2022.

- ^ Crothers, Brooke (August 23, 1996). "Intel and Cyrix duel for MMX". Cnet. Retrieved April 25, 2022.

- ^ Slater, Michael (1996). Cyrix Doubles 6x86 Performance with M2; MMX Added to Core; Larger Cache, Modified TLB Improve Scaling with Clock (PDF). Vol. 10. Microprocessor Forum (published October 28, 1996). pp. 1–3. Archived (PDF) from the original on December 2, 2021. Retrieved April 4, 2022.

- ^ a b Crothers, Brooke (January 2, 2002). "National Semi leaving PC chip market". Cnet. Retrieved April 11, 2022.

- ^ "National Semiconductor To Acquire Cyrix". Business Standard. July 30, 1997. Retrieved April 11, 2022.

- ^ Thurrott, Paul (July 27, 1997). "National Semiconductor buys Cyrix". ITPro Today. Retrieved April 11, 2022.

- ^ "Intel's strongest competitor in history was not amd for a long time". China IT. November 27, 2020. Retrieved April 11, 2022.

- ^ "National Produces First Functional Cyrix .25 Micron 6x86MX™ CPU". January 12, 1998. Retrieved April 12, 2022.

- ^ Kanellos, Michael (August 26, 1998). "National starts making Cyrix chips; National Semiconductor has also begun producing the Cyrix-brand chips with the advanced 0.25-micron manufacturing process". Cnet. Retrieved May 6, 2022.

- ^ "NATIONAL SEMICONDUCTOR HALTING I.B.M. AGREEMENT". The New York Times. September 26, 1998. Retrieved April 25, 2022.

- ^ "National Semi Dumps Big Blu". Wired. September 25, 1998. Retrieved April 25, 2022.

- ^ DiCarlo, Lisa (September 2, 1998). "IBM to stop making Cyrix chips". ZDNet. Retrieved April 25, 2022.

- ^ Kalish, David (September 25, 1998). "National Semi Ends IBM Chip Deal". CBS News. Retrieved April 25, 2022.

- ^ Tessler, Joelle (September 25, 1998). "National Semi's Unit Breaks Off Manufacturing Deal With IBM". The Wall Street Journal. Retrieved April 25, 2022.

- ^ Shimpi, Anand (May 26, 1998). "Cyrix M-II 300". Anandtech. Retrieved April 4, 2022.

- ^ Magee, Mike (December 7, 1998). "Cyrix takes axe to high-end MII prices; Battle to replace Intel after it dropped low end parts". The Register. Retrieved April 8, 2022.

- ^ Fisher, Lawrence (May 10, 1999). "National Semiconductor Quits the PC Chip Business". The New York Times. Retrieved April 11, 2022.

- ^ Carroll, Mark (June 30, 1999). "Via Technologies to acquire Cyrix". EETimes. Retrieved April 8, 2022.

- ^ Mueller, Scott (2003). "Cyrix/IBM 6x86 (M1) and 6x86MX (MII)". Upgrading and Repairing PCs. Que. pp. 175–176. ISBN 9780789729743. Retrieved April 8, 2022.

- ^ Hachman, Mark (November 17, 1999). "Via Technologies' Samuel microprocess or to anchor 2000 chip lineup". EETimes. Retrieved April 26, 2022.

- ^ Hachman, Mark (November 17, 1999). "Via Technologies' Samuel microprocessor to anchor 2000 chip lineup". EETimes. Retrieved April 26, 2022.

- ^ "Ellison's Net computer gets a pricey accessory". CNet. January 2, 2002. Retrieved April 26, 2022.

- ^ "VIA Cyrix® MII™". June 25, 2003. Archived from the original on June 25, 2003. Retrieved April 26, 2022.

- ^ a b "Cyrix M1 datasheet" (PDF). Cyrix.

- ^ This article is based on material taken from Cyrix+6x86 at the Free On-line Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later.

- ^ a b c "IBM 6x86MX datasheet" (PDF). Archived (PDF) from the original on January 30, 2014.

- ^ Phillips, Jon (July 2000). "The Pre-Fab Debate Continues". Maximum PC. Vol. 5, no. 7. Future US, Inc. p. 16. ISSN 1522-4279. Retrieved April 5, 2022.

- ^ Mury, John. "CPU Considerations; Cyrix". NiNe's Rendition Quake Workshop. Retrieved April 7, 2022.

- ^ Hsieh, Paul (September 7, 1999). "6th Generation CPU Comparisons; The Cyrix 6x86MX". Retrieved April 7, 2022.

Further reading

[edit]- Gwennap, Linley (October 25, 1993). "Cyrix Describes Pentium Competitor" Microprocessor Report.

- Gwennap, Linley (December 5, 1994). "Cyrix M1 Design Tapes Out". Microprocessor Report.

- Gwennap, Linley (June 2, 1997). "Cyrix 6x68MX Outperforms AMD K6". Microprocessor Report.

- Slater, Michael (February 12, 1996). "Cyrix, IBM Push 6x86 to 133 MHz". Microprocessor Report.

- Slater, Michael (October 28, 1996). "Cyrix Doubles x86 Performance with M2". Microprocessor Report.

External links

[edit]- Cyrix 6x86 ("M1") at PCGuide at the Wayback Machine (archived June 22, 2017)

- Cyrix 6x86 ("M1") at PCGuide

- cpu-collection.de Cyrix 6x86 processor images and descriptions

- Paul Hsieh's 6th Generation x86 CPU Comparison in-depth analysis of 6th generation x86 CPUs, including the 6x86MX.

- Cyrix M1 stats at Sandpile.org